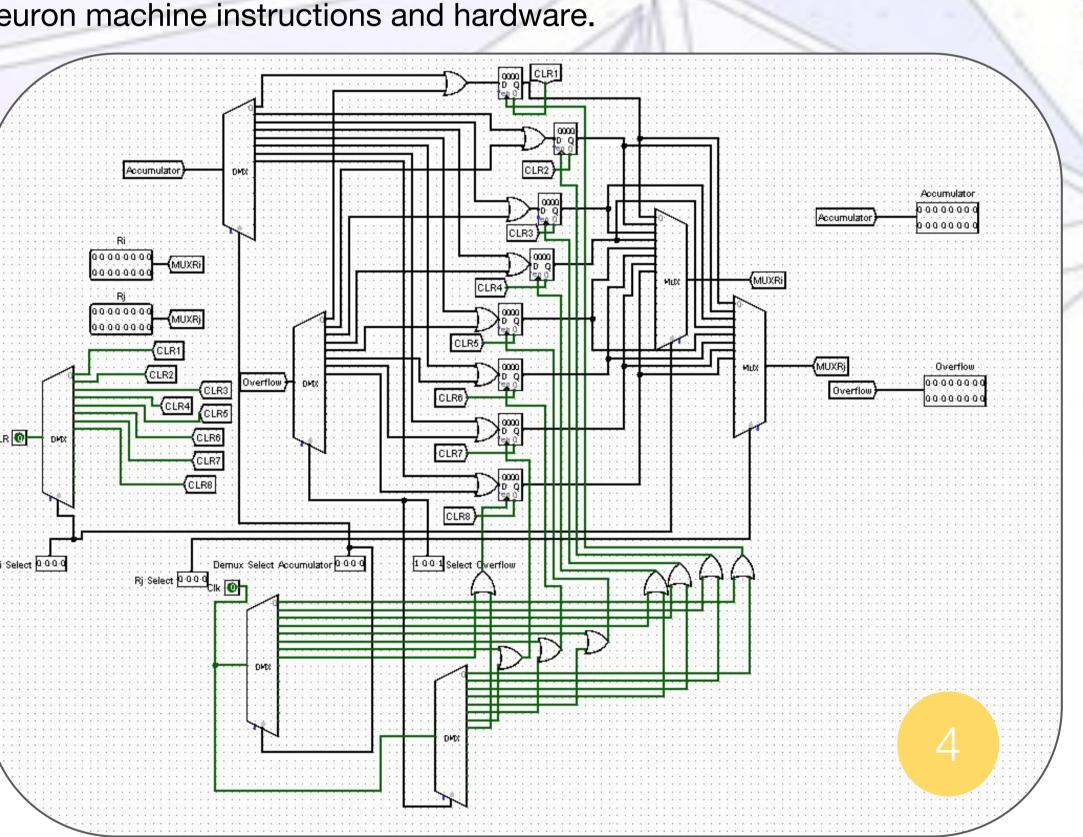

- implements the simple pipeline of fetch, decode, execute, and write-back; plus any special states.

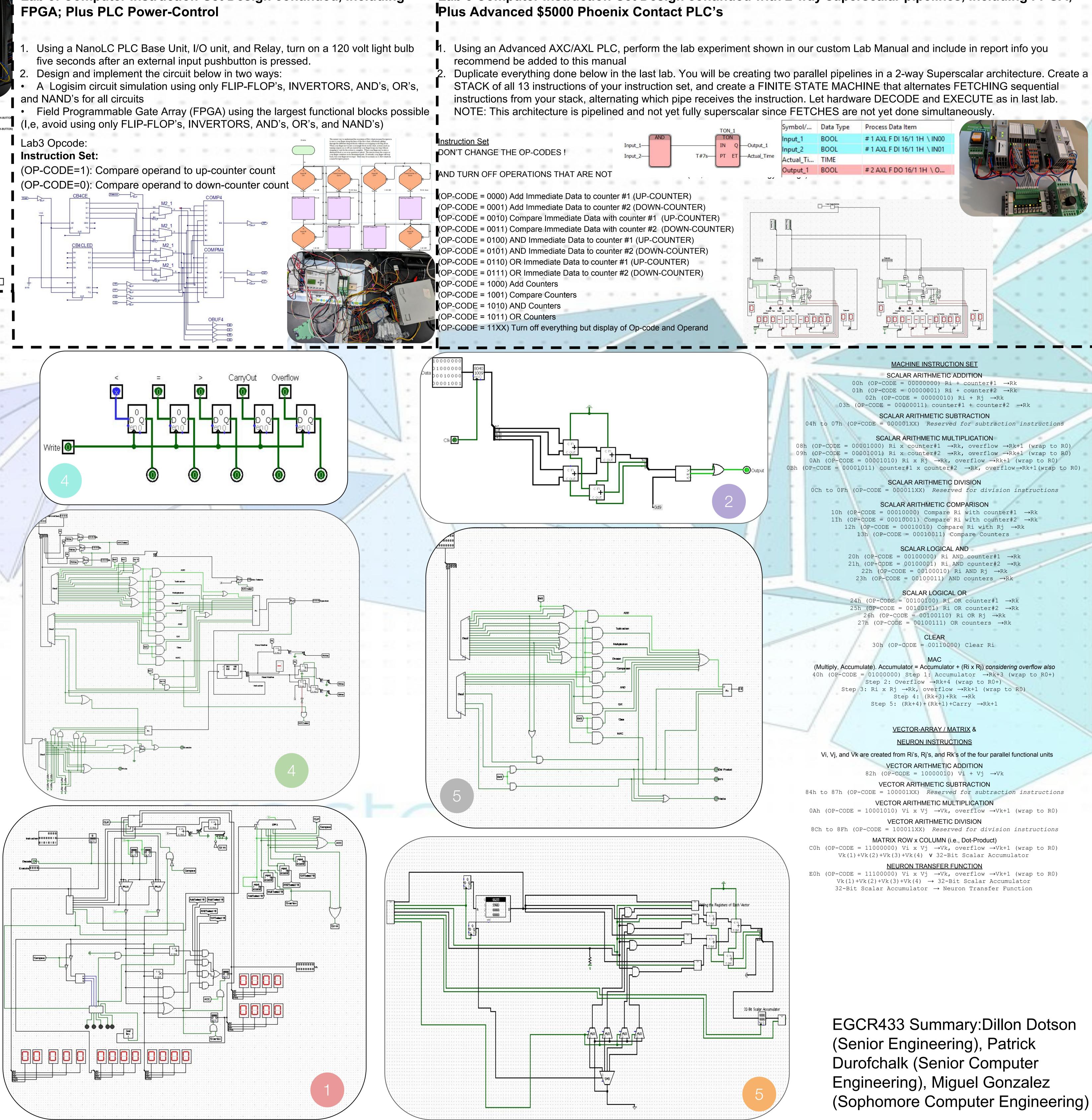

- 5. Then embed a carefully crafted assembly language code segment to demonstrate the functionality of your instruction set and circuitry in the minimal amount of time that you can defend as providing comprehensive testing of all scalar, vector, matrix, and neuron machine instructions and hardware.

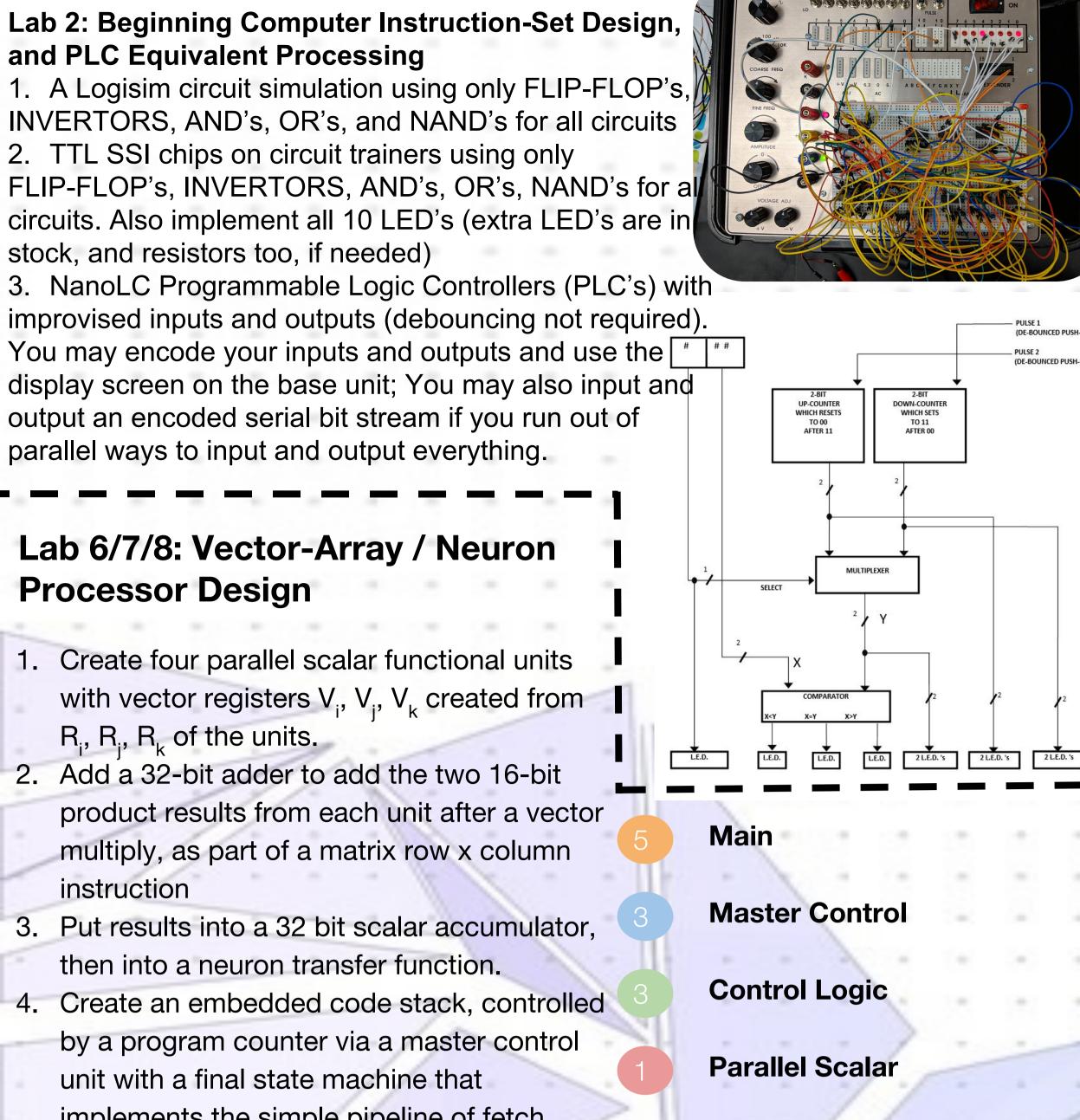

**Neuron Transfer Function**

**Execute Step**

**Register Bank**

**Status Register**

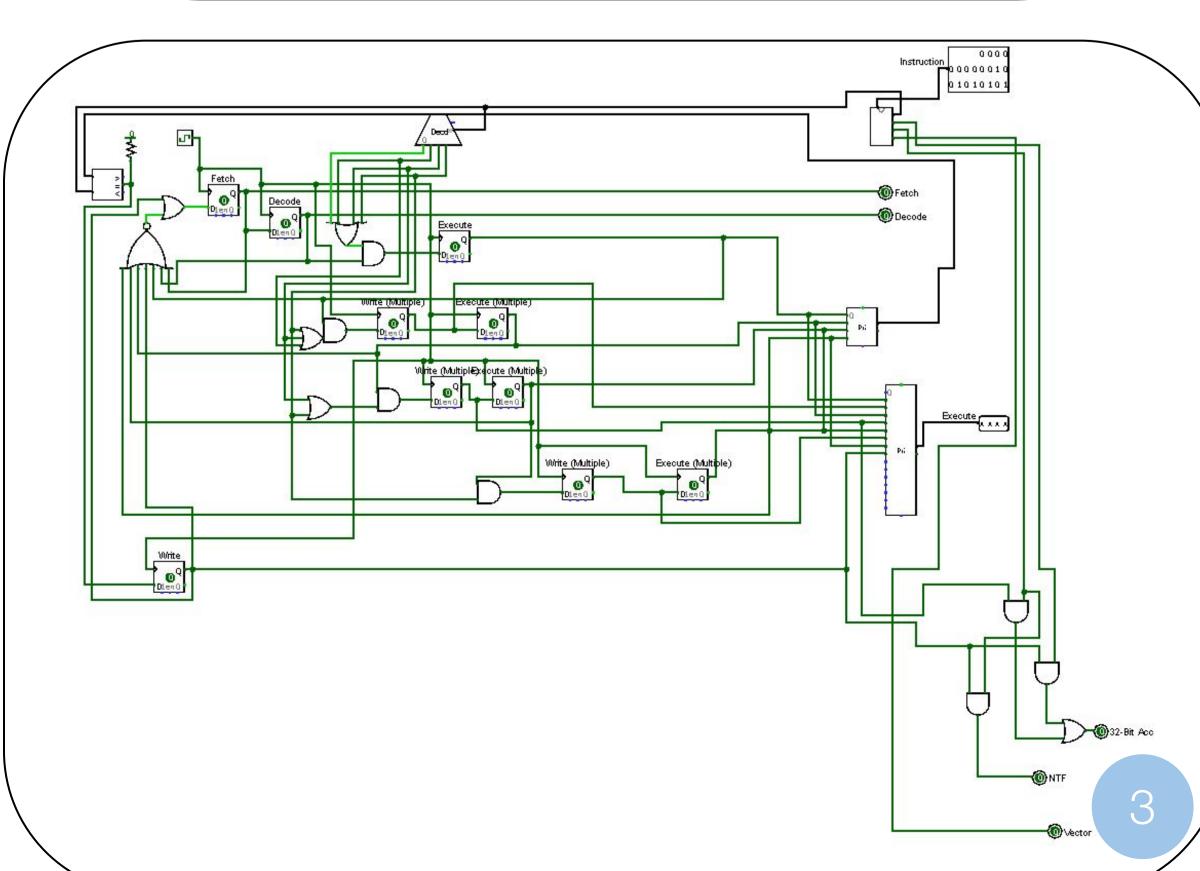

## Lab 3: Computer Instruction-Set Design continued, including **FPGA**; Plus PLC Power-Control

## Lab 5 Computer Instruction-Set Design continued with 2-way superscalar pipelines, including FPGA;