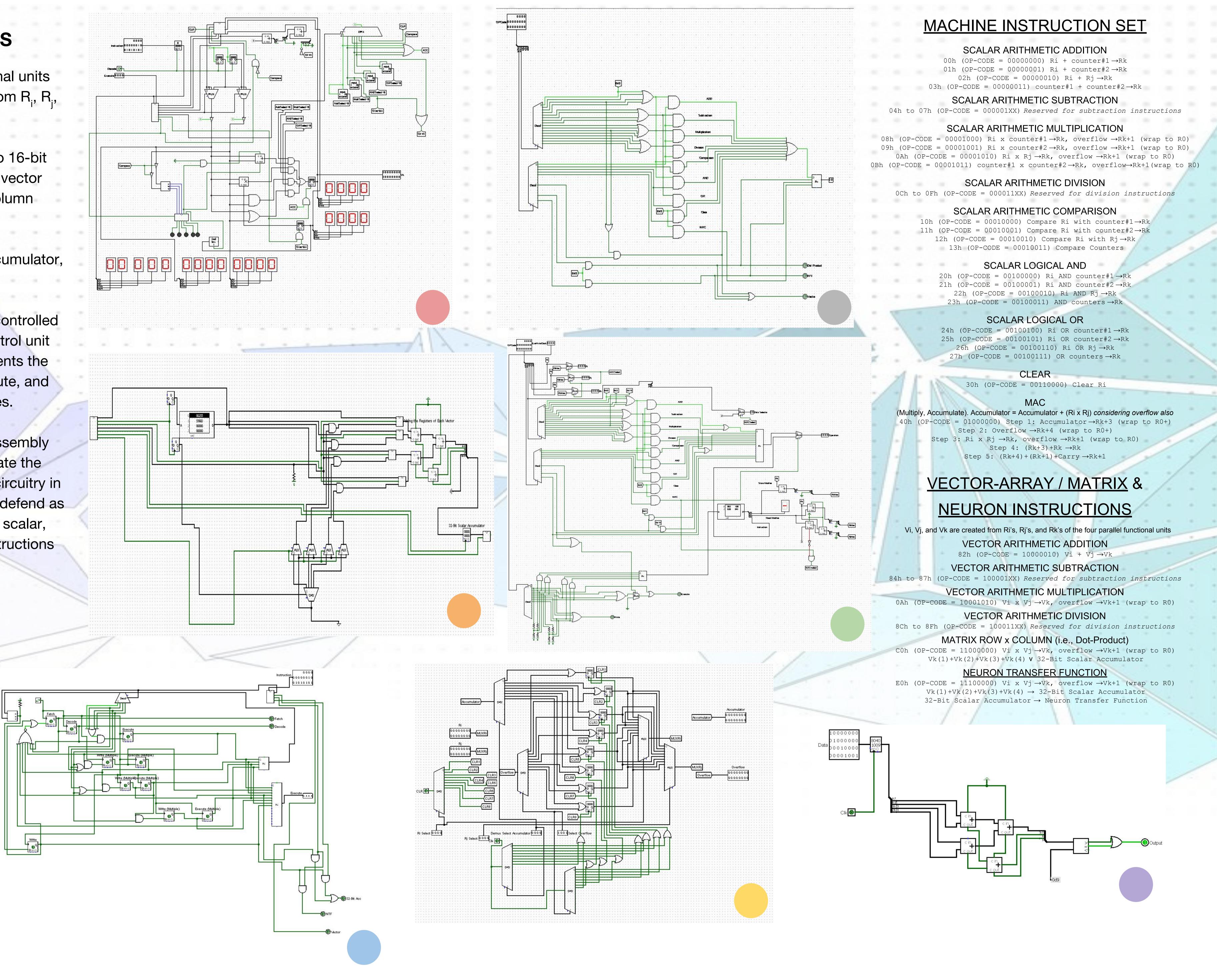

## **DESIGN REQUIREMENTS**

1. Create four parallel scalar functional units with vector registers V<sub>i</sub>, V<sub>i</sub>, V<sub>k</sub> created from R<sub>i</sub>, R<sub>i</sub>,  $R_{\nu}$  of the units.

2. Add a 32-bit adder to add the two 16-bit product results from each unit after a vector multiply, as part of a matrix row x column instruction

3. Put results into a 32 bit scalar accumulator, then into a neuron transfer function.

4. Create an embedded code stack, controlled by a program counter via a master control unit with a final state machine that implements the simple pipeline of fetch, decode, execute, and write-back; plus any special states.

5. Then embed a carefully crafted assembly language code segment to demonstrate the functionality of your instruction set and circuitry in the minimal amount of time that you can defend as providing comprehensive testing of all scalar, vector, matrix, and neuron machine instructions and hardware.

| 5 | Main                     |

|---|--------------------------|

| 3 | Master Control           |

| 3 | Control Logic            |

| 1 | Parallel Scalar          |

| 2 | Neuron Transfer Function |

| 5 | Execute Step             |

|   | Register Bank            |

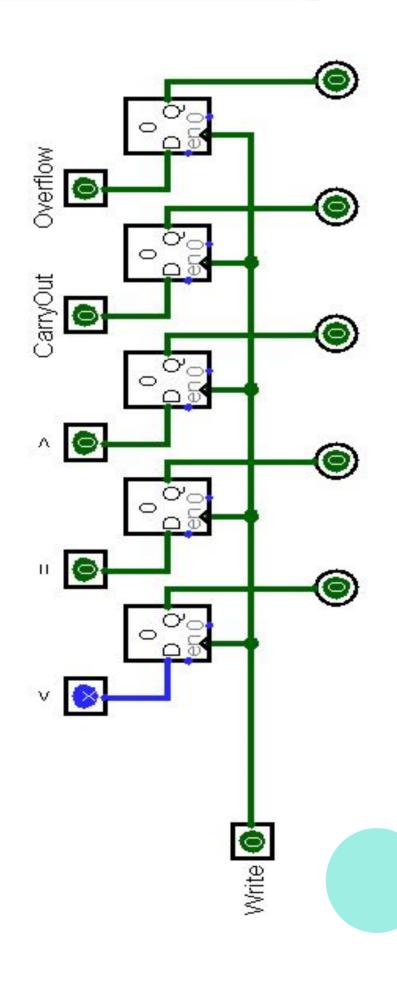

Status Register

Dillon Dotson (Senior Engineering), Patrick Durofchalk (Senior Computer Engineering), Miguel Gonzalez (Sophomore Computer Engineering)

Vector-Array / Neuron Processor Design