## ATOMS & TRANSISTORS (and GATES, and "CHIPS" - actually chip-"Packages")

by JT Wunderlich PhD

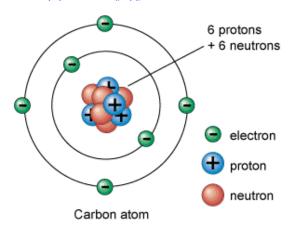

**<u>ATOM</u>**: Smallest particle of a substance that can exist by itself or be combined with other atoms to form a molecule **<u>MOLECULE</u>**: Smallest particle of a substance that retains all properties of the substance and is composed of one or more atoms

From: <u>http://www.merriam-webster.com/dictionary/atom</u> :

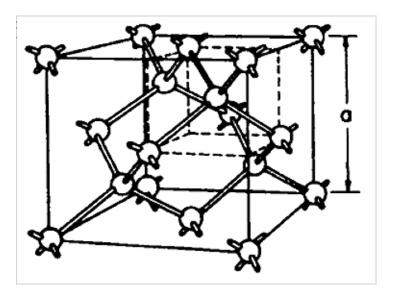

<u>**CRYSTAL LATTICE STRUCTURE</u>**: a unique arrangement of <u>atoms</u> or <u>molecules</u> in a <u>crystalline liquid</u> or <u>solid</u>.<sup>[11]</sup> A crystal structure describes a highly ordered structure, occurring due to the intrinsic nature of molecules to form symmetrical patterns. A crystal structure can be thought of as an infinitely repeating array of 3D 'boxes', known as unit-cells. *From <u>http://en.wikipedia.org/wiki/Crystal\_structure</u></sub></u>*

Anatomy of an Atom (Bohr Model); electrons circling a nucleus containing protons and neutrons. *From:* <u>http://www.freethought-forum.com/forum/showthread.php?t=24978&garpg=2</u>

Electrons are in *shells* (*Energy Levels*) around nucleus, with a certain number of electrons that fit into each shell. The outer shell is called the **valence shell**.

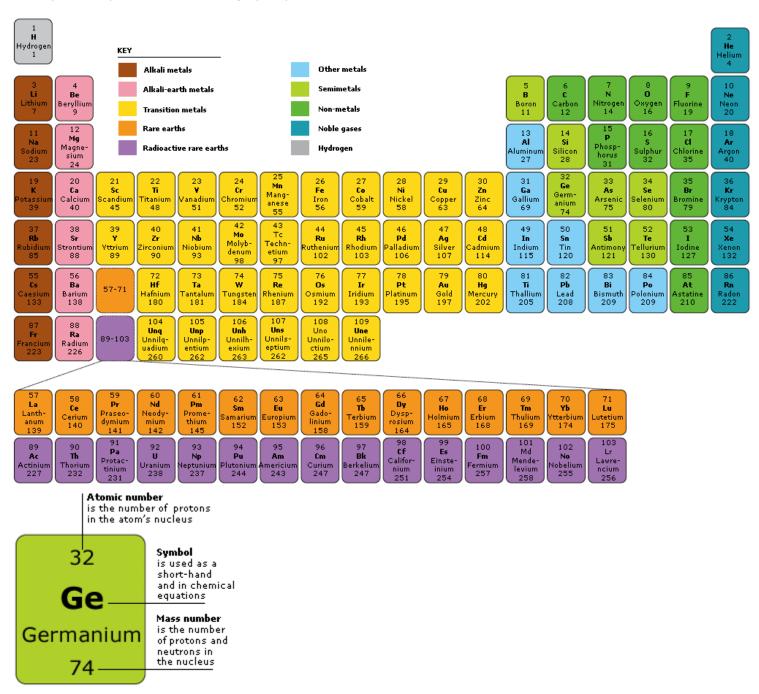

PERIODIC TABLE is a grid of every element that exists, arranged in order of atomic number, the number of protons each atom has in its nucleus. The <u>rows are called PERIODS and all have the same number of shells</u>; and the <u>columns called GROUPS which all</u> <u>have the same number of electrons in their outermost shell</u>. Hydrogen (H) is the first element because it has just one proton in its nucleus. Helium (He) is second, because it has two. As you go across a period, atoms get heavier, but also get smaller because the number of electron shells stays the same across the period, but the number of protons in the nucleus increases. The stronger, attractive force from the positively charged protons sucks the negatively charged electrons tighter into the centre.

A SEMICONDUCTOR can be either a single element (like Silicon, Si), or a compound (like Galium Arsenide, GaAs) Semiconductors are not conductors of electricity like gold (a metal), and not an insulator which prevents electricity from flowing. Semiconductors are useful because they can be "doped" to control electrical properties and to make transistors, the basic building blocks of computers.

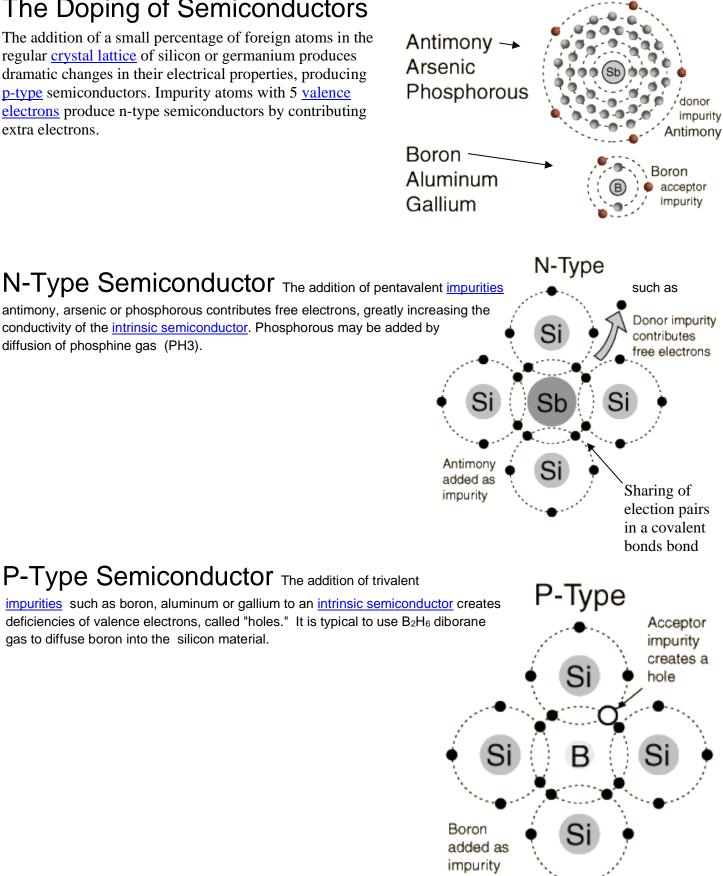

# The Doping of Semiconductors

The addition of a small percentage of foreign atoms in the regular crystal lattice of silicon or germanium produces dramatic changes in their electrical properties, producing p-type semiconductors. Impurity atoms with 5 valence electrons produce n-type semiconductors by contributing extra electrons.

diffusion of phosphine gas (PH3).

gas to diffuse boron into the silicon material.

From: http://hyperphysics.phy-astr.gsu.edu/hbase/solids/dope.html#c3 :

#### Silicon LATTICE STRUCTURE (un-Doped)

From: http://www.irf.com/technical-info/guide/semi.html

# Silicon LATTICE STRUCTURE (Doped) From: https://sites.google.com/site/reeetech/home/photovoltaic/silicon-cell

### Combine N and P type materials to make Transistors (and Diodes)

From: http://content.aviation-safety-bureau.com/allmembers/faa-h-8083-31-amt-airframe-vol-2/sections/chapter-11.php

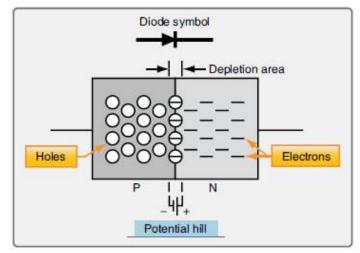

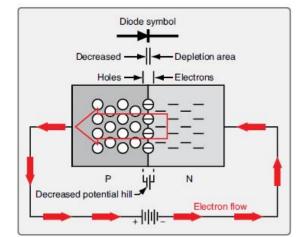

Figure 11-20. The flow of current and the P-N junction of a semiconductor diode attached to a battery in a circuit.

Figure 11-19. A potential hill.

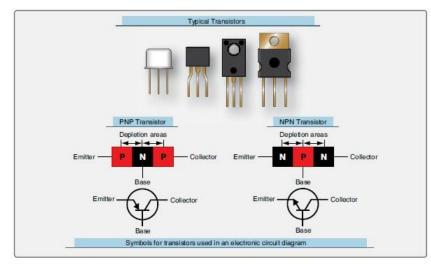

Figure 11-26. Typical transistors, diagrams of a PNP and NPN transistor, and the symbol for those transistors when depicted in an electronic circuit diagram.

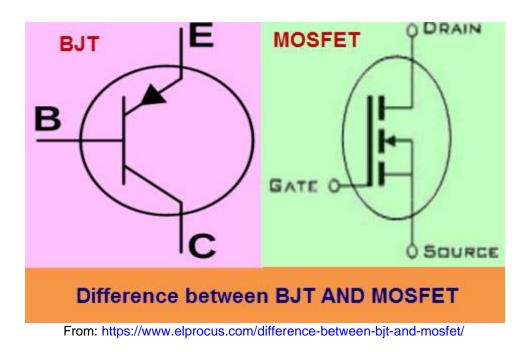

NOTE: This is one kind of transistor, called a **Bipolar** Junction Transistor (BJT)

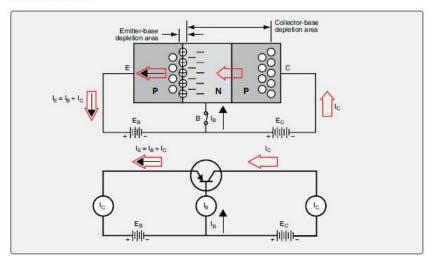

Figure 11-27. The effect of applying a small voltage to bias the emitter-base junction of a transistor (top). A circuit diagram for this same transistor (bottom).

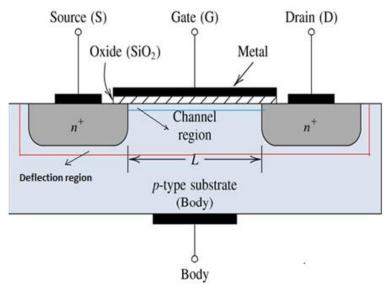

## Another type of Transistor is a Field Effect Transistor (FET)

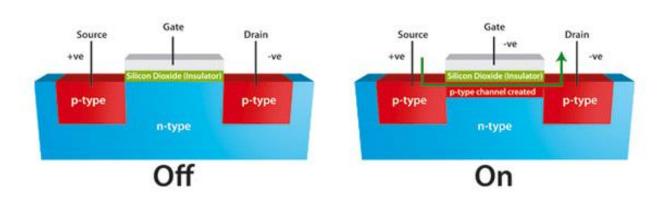

When a voltage is applied to the gate, a magnetic FIELD is created below the gate, which creates a conducting channel between the Source and Drain.

From: <u>http://www.rignitc.com/mosfets/</u>

These are called Metal Oxide Semiconductors (MOS), i.e., <u>MOSFET</u>'s From: <u>https://www.elprocus.com/mosfet-as-a-switch-circuit-diagram-free-circuits/</u>

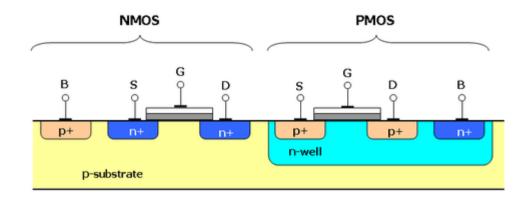

p-MOS has an N substrate, and n-MOS has a P substrate; and they are combined to make CMOS (i.e., Complementary Metal Oxide Semiconductor) circuits From: https://allthingsvlsi.wordpress.com/2013/04/04/nmos-and-pmos-operating-regions/

# Most important things know about transistors in Dr. Wunderlich's introductory Tech course:

• BJT

(Bipolar Junction Transistor)

• Functionality:

Apply small current from Base(B) to Collector(C) to get larger current from Emitter(E) to Collector(C)

• <u>5 VOLTS</u>

# • MOSFET

(Metal-Oxide-Semiconductor Field-Effect-Transistor) Functionality:

Apply voltage to Gate(G) to create a magnetic field that creates a conducting channel between the Source(S) and the Drain(D), allowing current to flow between S and D

• Typically <u>3.3 VOLTS</u> (but also 5 volts sometimes)

CMOS (2.5, <u>3.3</u>, 5, up to 18 volts)

# vs. BiPolar (<u>5</u> volts) Transistor Circuits

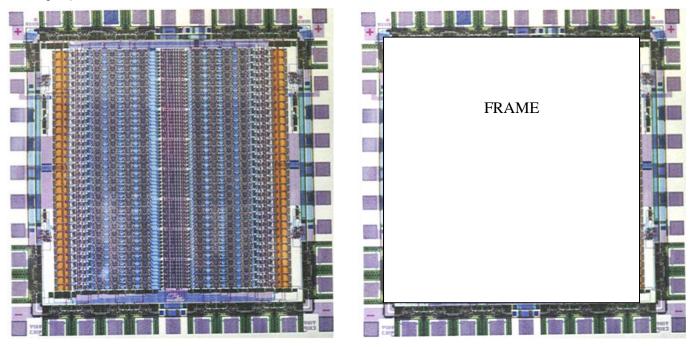

#### Artificial Dendrite Tree Neural Network Chip

(J. Wunderlich 1992 - his 2<sup>nd</sup> Neural Network Processor)

(5 volt CMOS Logic) in a 5 volt Frame (pad circuits for pin connections) supplied by "Mosis Tiny-chip" Manufacturer (USC)

Chip Pin-Out circuits can be either special CMOS (Complimentary Metal Oxide Semiconductor) FET's (Field Effect Transistors) or BiPolar BJT's (BiPolar Junction Transistors) to source more output current and to absorb more input voltage spikes

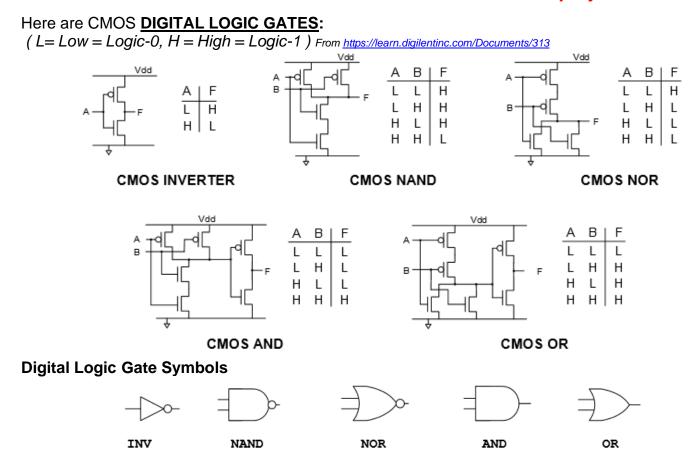

## Integrated Circuits (IC's) "CHIPS" of DIGITAL LOGIC GATES

used in Dr. Wunderlich's courses with Lab projects

Made with either BJT's (usually in TTL circuits, i.e., Transistor-Transistor-Logic) or with FET's in CMOS circuits.

The following is from <u>http://www.engr.uconn.edu/~zshi/course/cse2300/lecture2\_gates.pdf</u> : CMOS families:

- 4000 series

- 7400 series:

- 74HC (high-speed CMOS),

- 74HCT(High-speed CMOS, TTL compatible)

- 74AC(Avanced CMOS)

- 74ACT(Advanced CMOS, TTL compatible)

- 74FCT(Fast CMOS, TTL compatible)

- 74FCTT(Fast CMOS, TTL compatible with TTL

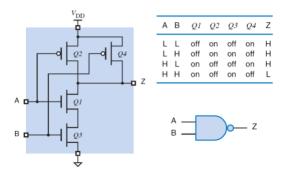

#### CMOS NAND gate

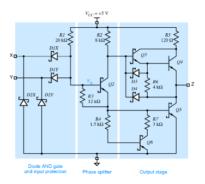

#### BiPolar Transistors Example of LS-TTL gates: 2-input NAND

Dr Wunderlich's E273 lab is equipped various **TTL** (Transistor-Transistor-Logic) SSI (Small Scale Integration) IC's (Integrated Circuit) "Chips". Below is a list of IC's usually found in the lab, Remember that TTL chips require 5Volts DC to operate (unlike CMOS chips used for the old radio shack circuit trainer found in the lab)

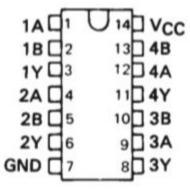

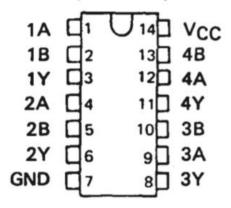

#### 2 Input OR (SN74LS32N):

| •      | · /            |

|--------|----------------|

| 1A 🗍   |                |

| 1B 🗖 2 | 13 4B          |

| 1Y 🗖 3 | 12 🗖 4 A       |

| 2A 🛛 4 | 11 4Y          |

| 2B 🗋 5 | 10 <b>]</b> 3B |

| 2Y 🗖 6 | 9 <b>]</b> 3A  |

| GND 7  | 8 3Y           |

|        |                |

3 Input OR (CD74HC4075E):

#### 4 Input OR (CD4072BE):

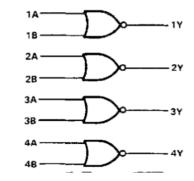

### 2 Input NOR (SN7402N):

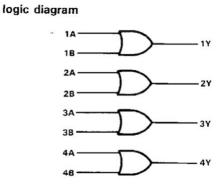

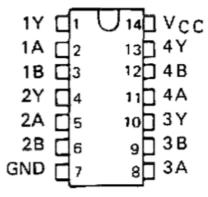

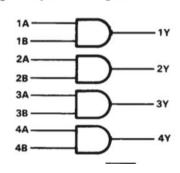

2 Input AND (SN74LS08N):

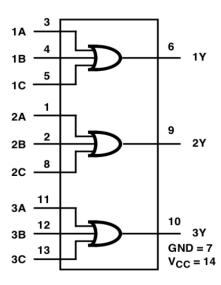

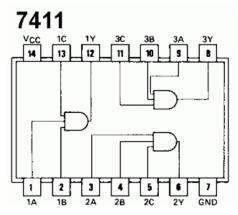

### 3 Input AND:

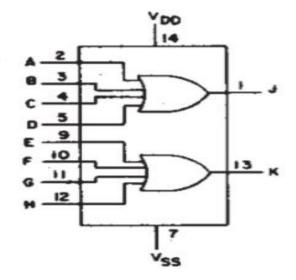

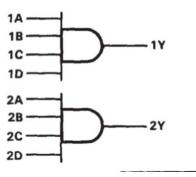

### 4 Input AND (SN74LS21N):

#### logic diagram

logic diagram (positive logic)

logic diagram (positive logic)

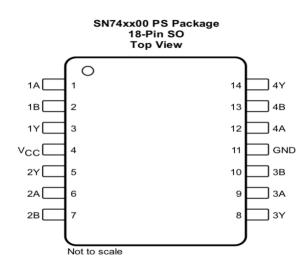

#### 2 Input NAND (SN74LS00N):

Logic Diagram, Each Gate (Positive Logic)

Υ

Α

В

#### 3 Input NAND (SN74LS10N):

| (TOP VIEW) |        |       |  |

|------------|--------|-------|--|

|            | 1 U 14 | ⊐ vcc |  |

| 1В 🗋       | 2 13   | ] 1C  |  |

| 2A 📮       | 3 12   | ] 1Y  |  |

| 2в 🗋       | 4 11   | ] 3C  |  |

| 2C 🗖       | 5 10   | ] 3B  |  |

| 2Y 🗋       | 69     | ] 3A  |  |

|            | 78     | ] 3Y  |  |

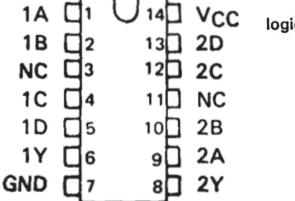

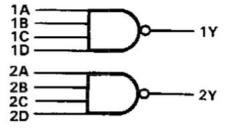

4 Input Quad NAND (74LS20):

#### logic diagram

| 1 <b>A</b> | Цī       |                |

|------------|----------|----------------|

| 1B         |          | 13 2D          |

| NC         | ₫3       | 12 2C          |

| 1C         | ₫₄       | 11 NC          |

| 1D         | đ۶       | 10 <b>] 2B</b> |

| 1Y         | <b>6</b> | 9] 2A          |

| GND        | d۶       | 8 2 Y          |

## 2 Input XOR (SN74LS86AN):

These are five equivalent Exclusive-OR symbols valid for an '86 or 'LS86A gate in positive logic; negation may be shown at any two ports.

LOGIC IDENTITY ELEMENT

The output is active (low) if all inputs stand at the same logic level (i.e., A = B).

The output is active (low) if an even number of inputs (i.e., 0 or 2) are active.

EVEN-PARITY

\_\_\_\_\_2k+1

The output is active (high) if an odd number of inputs (i.e., only 1 of the 2) are active.

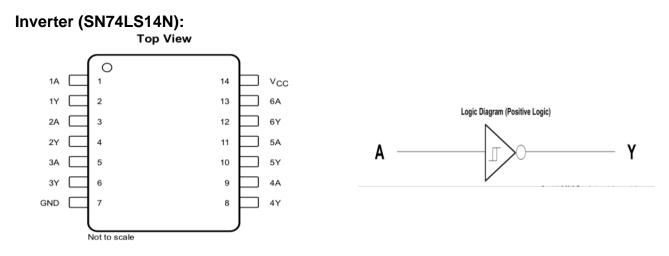

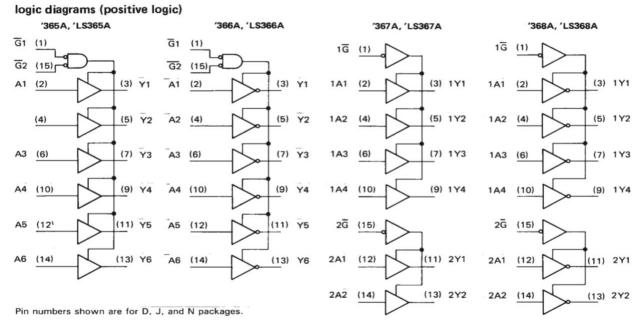

#### Hex Busdriver with 3-State Outputs (74367AN):

**A1**

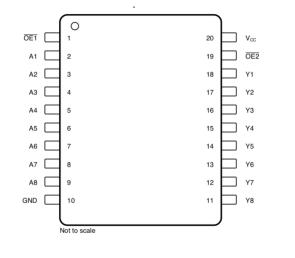

#### Buffer/Drivers 3-States (SN74HC541N):

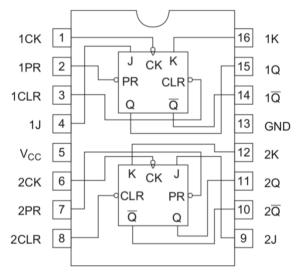

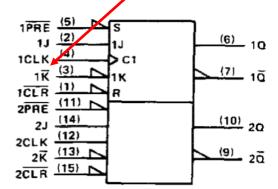

#### JK Flip Flop (HD74LS76AP):

## JK Naught (i.e., J\_not-K Flip Flop (SN74LS109AN):

### D Flip Flop (SN74LS273N):

| -     | -  | - |    |                  |

|-------|----|---|----|------------------|

| CLR [ | 1  | U | 20 | ]v <sub>cc</sub> |

| 1Q [  | 2  |   | 19 | ] 8Q             |

| 1D [  | 3  |   | 18 | 8D               |

| 2D 🛛  | 4  |   | 17 | ] 7D             |

| 2Q 🛛  | 5  |   | 16 | ] 7Q             |

| 3Q [  | 6  |   | 15 | ] 6Q             |

| 3D [  | 7  |   | 14 | ] 6D             |

| 4D 🛛  | 8  |   | 13 | 5D               |

| 4Q [  | 9  |   | 12 | ] 5Q             |

| GND [ | 10 | ) | 11 | CLK              |

|       |    |   |    |                  |

#### DRAM (TMS425612N)

| A8 🖸                    | 1 | Ule | ]v <sub>ss</sub> |

|-------------------------|---|-----|------------------|

| ·р [                    | 2 | 15  | CAS              |

| $\overline{\mathbf{w}}$ | 3 | 14  | Ja               |

| RAS                     | 4 | 13  | ]A6              |

| A0 [                    | 5 | 12  | ]A3              |

| A2 🛛                    | 6 | 11  | ]A4              |

| A1 [                    | 7 | 10  | <b>A</b> 5       |

| VDD [                   | 8 | 9   | ]A7 -            |