IBM Hardware Development Engineer and Researcher (1996, 97, and 98)

IBM S/390 Hardware Development Lab, Poughkeepsie, NY

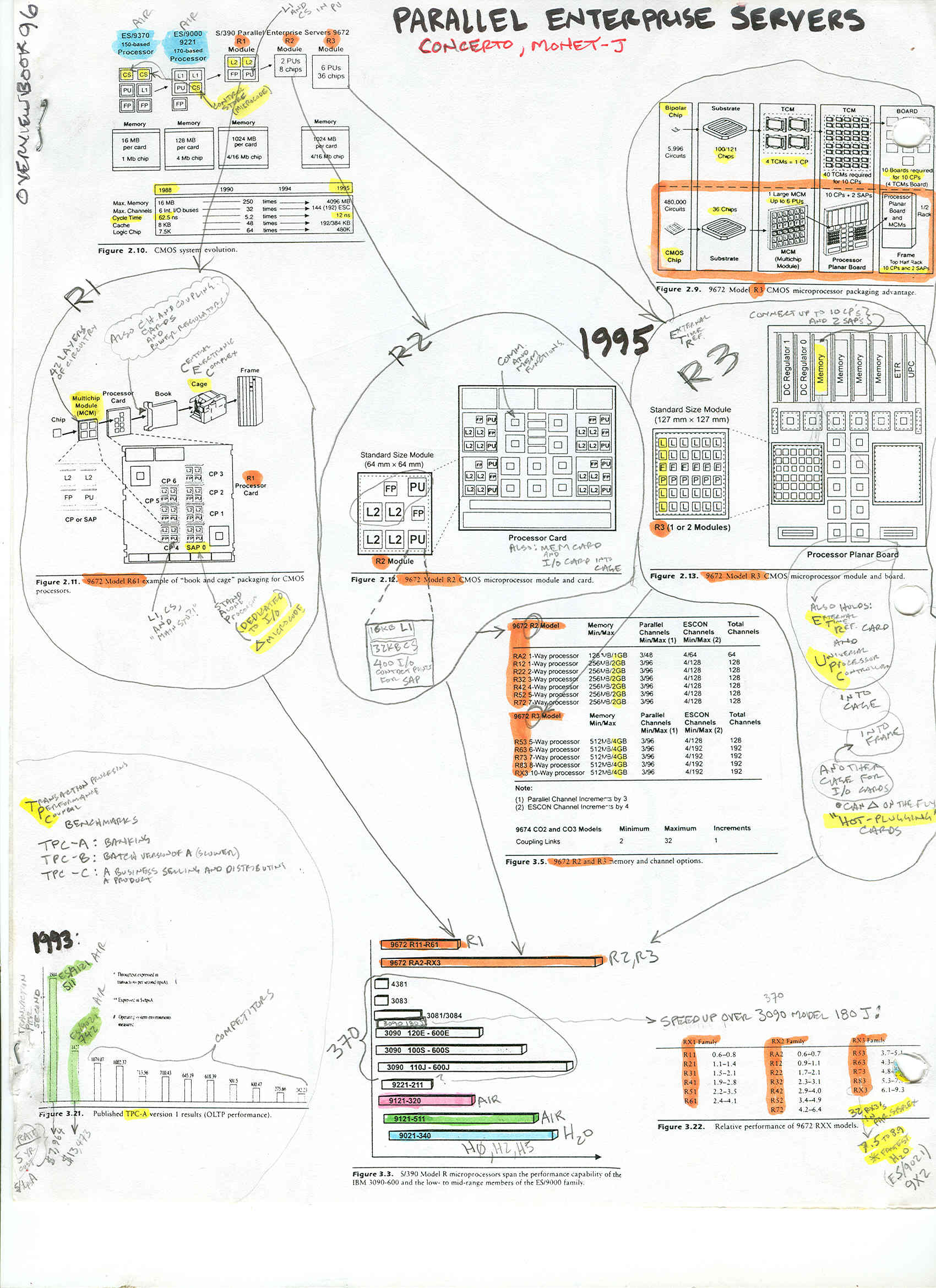

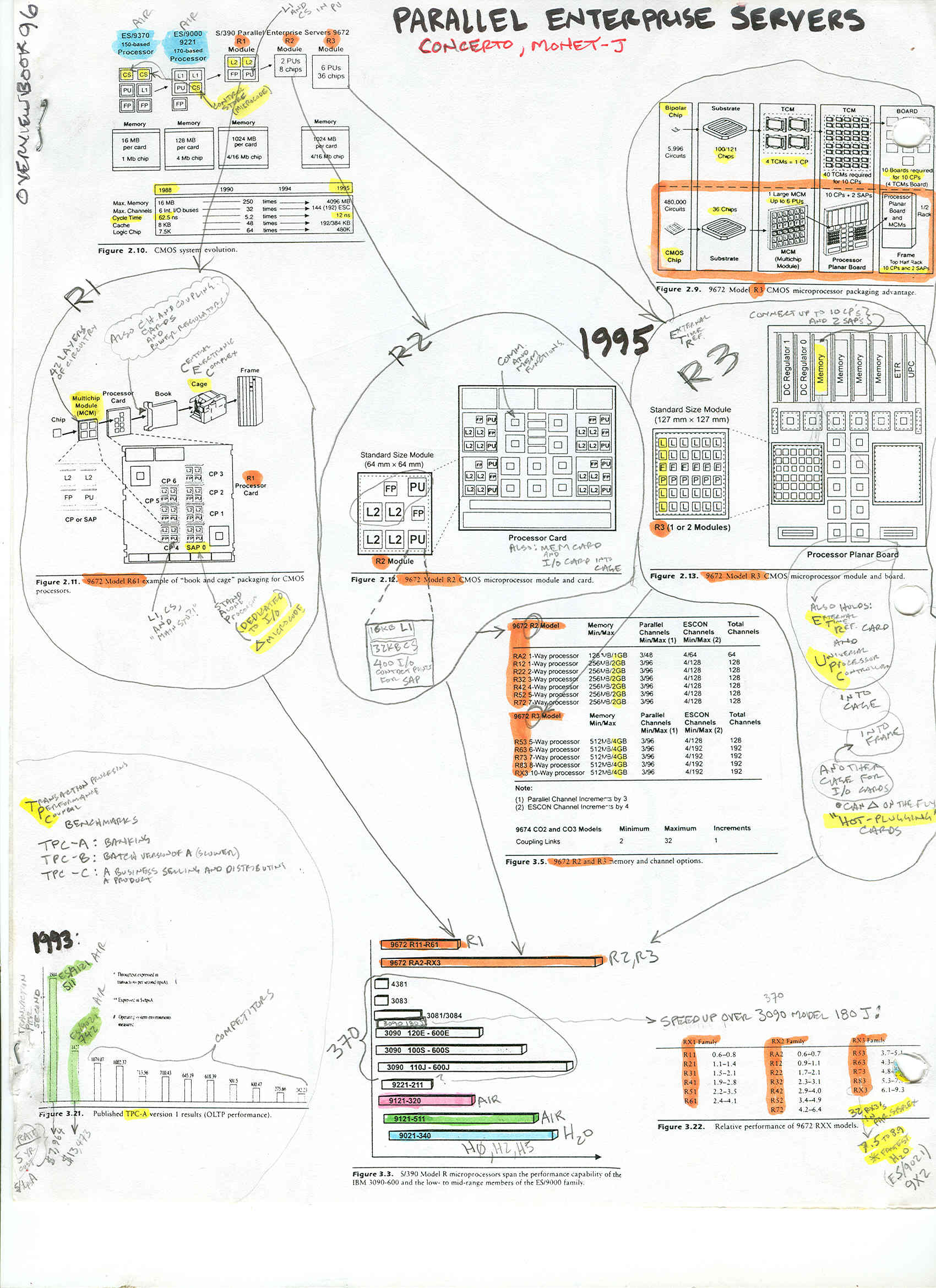

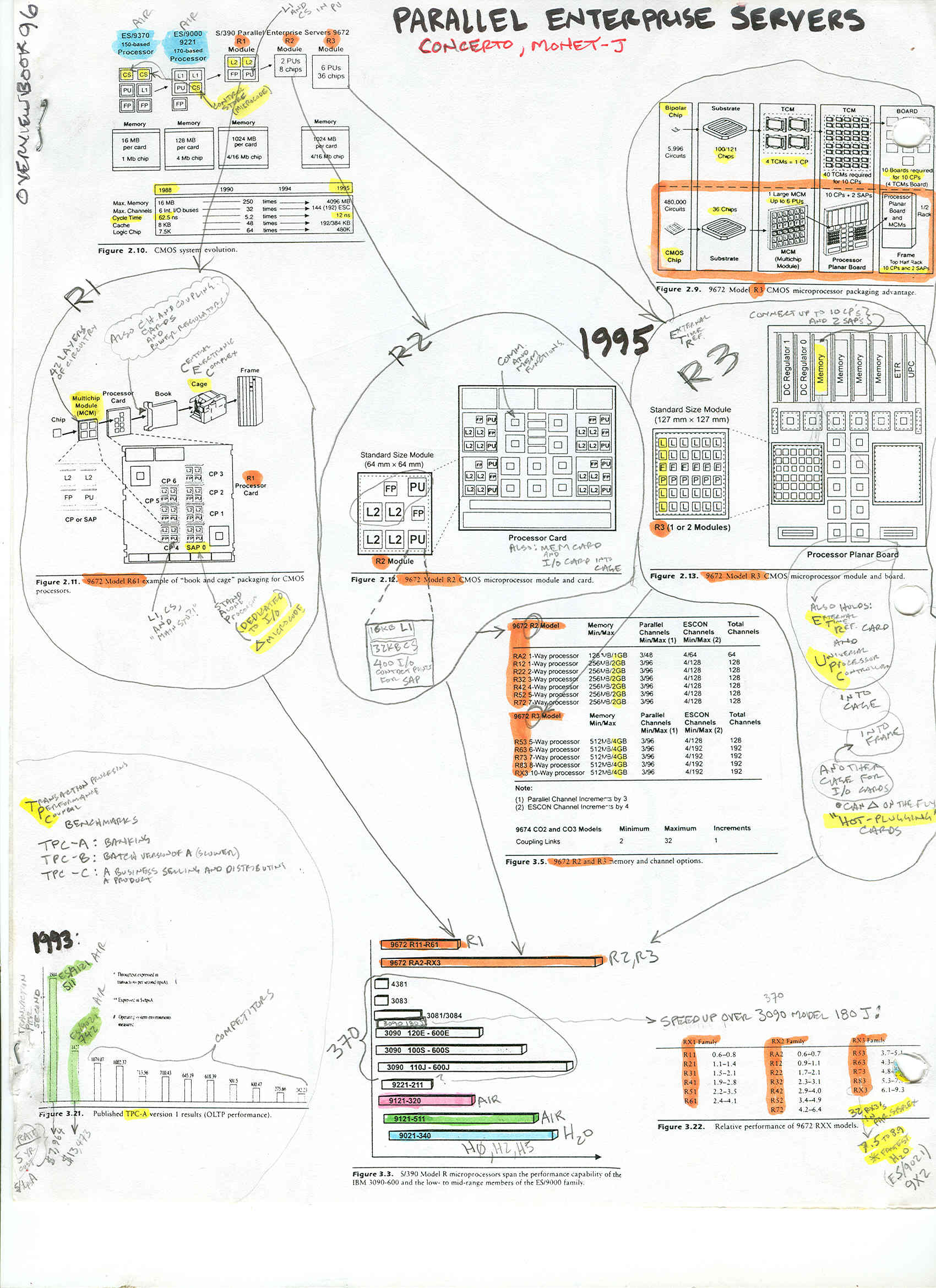

- Helped develop Symmetric Multi-Processor (SMP) mainframe-supercomputer architectures (jointly developed with IBM Germany) by engineering systems-level software and part of the SAK (Systems Assurance Kernel) operating system for QUALITY-CONTROL / VERIFICATION to "stress" features and force hardware failures through pseudo-random generation of correlated machine states and operating scenarios. Machines included 20 multicore processors (18 CPU and 2 I/O); divisible into 15 logical partitions and scalable to 512 processors to fit inside a $1M vending-machine size box; Scalable/connectable to other mainframes & supercomputers via a dynamic optical interconnect (IBM Parallel Sysplex). Engineered software to run in three environments: VLSI circuit simulation, prototype hardware test, and manufacturing. New 64-bit processing (address and data) required simulating 64-bit arithmetic and virtual-addressing to test simulated 64-bit prototype architectures using 32-bit machines. Prototypes were released as "IBM eServer zSeries" (now called IBM Z). My research included microprocessor branch-prediction verification strategies in a multiprocessor environment; and theory for hardware verification with seven correlated random number generators. My development projects included writing 20,000 lines of high-level language (PL/X) and S/390 assembly code including operating system application interfaces (API's). My RNG API code was also translated into C for IBM AS/400 minicomputers and RS-6000 (AIX type UNIX) workstations (the predecessor of POWER7 supercomputers like "Watson") requiring supervising an engineer in Austin TX via the IBM intranet. Other projects included verification programs for cache coherency, virtual addressing, space-switching, linkage control, and 125 new IEEE floating-point instructions (to supplement IBM Hex floating-point). All 1400 IBM S/390 machine instructions were tested (including vector-register instructions for add-on vector-register unit). A patent process was initiated for my random number theory and API's

These S/390 systems are now called IBM "Z")

IBM S/390 Multiprocessor Hardware at the beginning of Dr. Wunderlich's IBM research

(IBM internal code names "Concerto" and "Monet"):