Elizabethtown College Syllabus

EGR / CS 433

Advanced Computer Engineering LECTURE

Advanced Computer Engineering LAB

(Spring,

2020)

Advanced digital circuit

design and implementation. Major laboratory projects require students

to design, build, test, and demonstrate computer hardware. Class lectures

include design of embedded systems, microcontrollers, microprocessors, and

supercomputers. Cache designs, Parallel processing topics, Instruction set

designs, Neurocomputer designs. IBM research, and custom lab manuals.

*Prerequisite(s): EGR 332. Hours:

lecture 3, laboratory 3. Spring semester,

even-numbered years.

Professor: Joseph T Wunderlich PhD

Offices: E274E

and E273

Office: 717-361-1295 Cell: 717-368-9715

Email: wunderjt@etown.edu

Website: http://users.etown.edu/w/wunderjt

Office Hours & Calendar: http://users.etown.edu/w/wunderjt/schedules/CALENDAR3_s20_web.htm

Course Credit: 4

Contact Hours: 6 (therefore 6 x 50 = 300

minutes per week of “contact”)

Meeting Times

MF 3:30-5:50

Learning Objectives:

1.

Qualitative

and quantitative analysis and design of advanced computer architectures and

systems

2.

Gate-level

design of computer systems

3.

Hands-on

laboratory projects

Grading:

50% Laboratory projects

20% Midterm Exam

30% Comprehensive final exam

Attendance

& Participation is expected since you will have other people depending on

you, so up to –10% of course grade for excessive absences, tardiness, or lack

of class participation or preparedness; HOWEVER, IF

YOU ARE SICK, YOU MUST NOT COME TO CLASS

COURSE GRADE:

(60-62)=D-, (63-67)=D, (68-69)=D+,

(70-72)=C-, (73-77)=C, (78-79)=C+, (80-82)=B-, (83-87)=B, (88-89)=B+,

(90-92)=A-, (93-100)=A

(with

any fractional part rounded to the nearest integer)

Prerequisite

Topics:

·

Assembly

language (basic concepts) (Mandatory)

·

Computer

architecture (register-transfer level data-flow) (Mandatory)

·

Computer

architecture (gate-level data-flow and control) (Mandatory)

·

Combinational

digital circuit design (Mandatory)

·

Sequential

digital circuit design (Mandatory)

·

Analog

circuit design concepts (Recommended)

Disabilities

Elizabethtown College welcomes

otherwise qualified students with disabilities to participate in all of its

courses, programs, services, and activities. If you have a documented

disability and would like to request accommodations in order to access course

material, activities, or requirements, please contact the Director of Disability

Services, Lynne Davies, by phone (361-1227) or e-mail daviesl@etown.edu. If your documentation meets the college’s documentation

guidelines, you will be given a letter from Disability Services for each of

your professors. Students experiencing

certain documented temporary conditions, such as

post-concussive symptoms, may also qualify for temporary academic

accommodations and adjustments. As early as possible in the semester, set up an

appointment to meet with me, the instructor, to discuss the academic

adjustments specified in your accommodations letter as they pertain to my

class.

Class Cancelation

Any non-emergency class cancelation will be

announced via email at least a two hours before class time, in addition to signage

posted by Department Administrative Assistants. Any makeup work will be

announced to insure all intended course content is covered.

Religious Observations

The College is willing to accommodate individual religious beliefs and

practices. It is your responsibility to meet with the class instructor in

advance to request accommodation related to your religious observances that may

conflict with this class, and to make appropriate plans to make up any missed

work.

Academic Honesty

Elizabethtown College Pledge of Integrity: "Elizabethtown

College is a community engaged in a living and learning experience, the

foundation of which is mutual trust and respect. Therefore, we will strive to

behave toward one another with respect for the rights of others, and we promise

to represent as our work only that which is indeed our own, refraining from all

forms of lying, plagiarizing, and cheating." See the 2016-17 Elizabethtown College

Catalog, “Standards of Academic Integrity” (Academic Integrity at

Elizabethtown College, 11th ed. (https://www.etown.edu/offices/dean-of-students/files/academic-integrity-handbook.pdf).

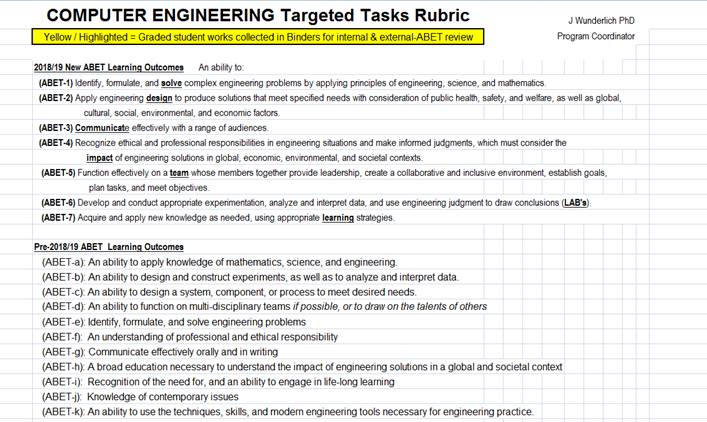

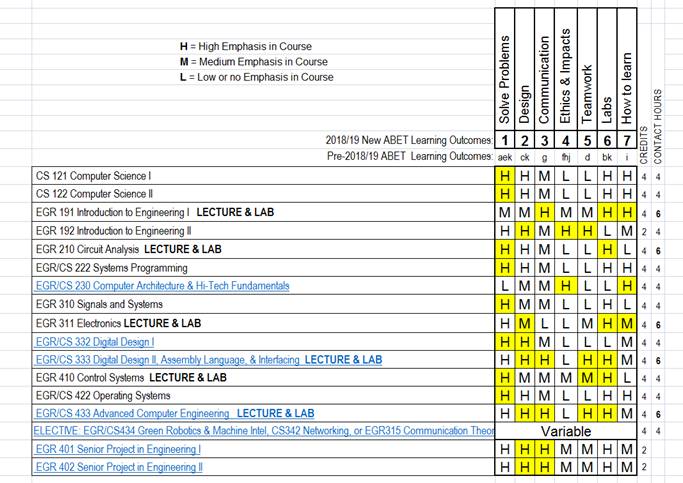

Learning

Outcomes

REQUIRED READINGS

A bound collection of reading

packets is a required purchase from the bookstore, and will contain these files

which are also available in my pulic folder, and on

my Computer Engineering page HERE:

PACKET 0 BOOKSTORE 433 COVER_SYLLABUS

PACKET 1 BOOKSTORE 433 Lecture

1 Supercomputer Fundamentals

PACKET 2 BOOKSTORE 433 Lecture

2 Part 1 Parallel Processing Fundamentals

PACKET 3 BOOKSTORE 433 Lecture

2 Part 2 Interconnect Architectures

PACKET 4 BOOKSTORE 433 Lecture 3 Part 1 Memory and Cache

PACKET 5

BOOKSTORE 433 Lecture 3 Part 2 Virtual Memory

PACKET 6

BOOKSTORE 433 Lecture 4 RISC vs CISC, Performance

PACKET 7

BOOKSTORE 433 Lecture 5 Dr W IBM OVERVIEW

PACKET 9

BOOKSTORE 433 Lecture 7 Dr W Machine Intelligence History

(Part

of draft book chapter)

PACKET 10

BOOKSTORE 433 Lecture 8 CALCULUS for Machine Learning

PACKET 11

BOOKSTORE 433 Lecture 9 Dr W Machine Learning Hardware Book Chapter

PACKET 12

BOOKSTORE 433 Lecture 10 2017 Supercomputer Paper

PACKET 14

BOOKSTORE 433 Lecture 12 SC-16H Computer Design by Glen G Langdon

PACKET 15 BOOKSTORE

433 Lab_0_2020

PACKET 16

BOOKSTORE 433 Chips_PSU_Trainer Lab Manual v1.2

PACKET 17

BOOKSTORE 433 2019 MANUAL FPGA

PACKET 18 BOOKSTORE 433 2019 MANUAL Relays

PACKET 19

BOOKSTORE 433 NanoLC Manual

PACKET 20

BOOKSTORE 433 2019 MANUAL AXC PLC

v0.0.6

PACKET 21

BOOKSTORE 433 2019 MANUAL 8051Microcontroller Simulator

PACKET 22

BOOKSTORE 433 2019 MANUAL Raspberry Pi v.2

and contains our custom lab manuals:

(written

by students, often edited by J. Wunderlich)

·

2018 IC's, Circuit Trainer, and Power Supply

·

2019 FPGA (2018B, 2018A, 2013, pre-2013)

·

2019 Advanced PLC (Phoenix Contact “Axiocontroller”)

·

2020 Advanced PLC (Phoenix Contact “PLCnext”) coming soon

·

2019 Intel 8051 Microcontroller (2015, 2014, Pre-2013)

·

2019 Rasberry Pi and ARM

Microcontroller

(subject to change throughout the semester)

Symmetric Multiprocessing (SMP)

Massively Parallel Processing (MPP)

GRAIN SIZE

Hardware vs. Software Parallelism

CONNECTIVITY ARCHITECTURES /TYPOLOGIES

Static

Dynamic

Scalability (and Probability of performance as connectivity increased)

Spatial and Temporal Locality of Reference

Probability of finding the most likely needed replacement data after a

Cache Miss

Probability of optimizing Hit-Miss Ratio

Replacement policy after a Cache Miss

Probabilistic, Least Recently Used, etc.

Calculus Review

Comparison of Instruction Sets (IBM S/390, MC 680XX,

PowerPC, Intel 8051, 80251, 8088, And PIC)

CISC (Complex Instruction-Set Computing)

RISC (Reduced Instruction-Set Computing)

SUPERCOMPUTER and NEUROCOMPUTER CASE STUDIES

Symmetric Multiprocessing (SMP)

IBM S/390 Vector-Register Unit and Instruction-Set

Massively Parallel Processing (MPP)

IBM Power-Parallel “Deep-Blue”

ARCHITECTURAL VERIFICATION OF

SUPERCOMPUTER DESIGNS BY CONTROLLED RANDOMNESS

Probability theory (IBM Research)

·

PHOTO’S OF ALL CIRCUITS (AND TEST-SET-UP’S BUILT) !

1. “Assignment”

(An exact copy of everything in this document -- exactly how it looks here)

2. “Equipment Used”

(A list of hardware and software) INCLUDE PHOTO’S OF ALL EQUIPMENT

4. “Options”

(if applicable, a comparison of each method used)

probability of satisfactory coverage by chosen test vectors

7. “References”

(in standard IEEE format)

8. “Appendices”

(for spec sheets, etc.)

For

Combinational Digital Logic Design:

Step

4: Find simplified function(s)

For

Sequential Digital

Logic Design::

Step

6: Append flip-flop inputs

Step

7: Find simplified function(s)

Step

10: Analyze any unused states

· COLOR-CODED LOGIC

DIAGRAMS are required for any digital circuit (Breadboard, FPGA, etc.)

· FLOW CHART

is required for any program

ASSIGNMENT: LAB #0 “Test Functionality of all Hardware and Software”

COURSE: EGR/CS433

“Advanced Computer Engineering Lecture & Lab”

SYLLABUS: http://users.etown.edu/w/wunderjt/syllabi/CS433%20Wunderlich,Joseph.htm

INSTRUCTOR: J

T Wunderlich PhD

LATE PENALTY: Minus 33.3% per class period for each

late item

Read all of our

existing custom Lab Manuals (This is all testable material):

·

2018 IC's, Circuit Trainer, and Power Supply

·

2019 FPGA (2018B, 2018A, 2013, pre-2013)

· 2019 Advanced PLC (Axiocontroller)

·

2019 Intel 8051 Microcontroller (2015, 2014, Pre-2013)

· 2019 Rasberry Pi and ARM

Microcontroller

GRADE PERCENTAGES and DUE DATES:

·

One simple Combinational, and one simple Sequential

Circuit

None Demonstrate Old

Circuit Trainer circuits

[primarily for 5 volt TTL chips]:

None Demonstrate RadioShack Circuit Trainer circuits [primarily for ~3 volt CMOS

chips]

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate Logisim Circuit simulations

·

One simple Combinational, and one simple Sequential

Circuit

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate Phoenix Contact NanoLC PLC simulations

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate Phoenix Contact NanoLC PLC real-time systems

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate

Phoenix Contact Advanced PLC (Axiocontroller)

No Demo, but see

Below Demonstrate

Phoenix Contact Advanced PLC (PLCnext)

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate Field Programmable Gate Array (FPGA) simulations

(10%) MONDAY 1/27/20 AT 3:30PM Demonstrate Field Programmable

Gate Array (FPGA) real-time systems

None Demonstrate

INTEL

8051/80251 or ARM microcontroller simulations

None Demonstrate INTEL 8051/80251 or

ARM microcontroller real-time systems

(10%) MONDAY

1/27/20 AT 3:30PM Demonstrate

Raspberry Pi real-time systems

(10%) MONDAY

1/27/20 AT 3:30PM Demonstrate Arduino

real-time systems

None Demonstrate Basic-Stamp real-time systems

None Demonstrate Direct PC-port real-time systems

None Demonstrate Remote mobile-device real-time systems

None Demonstrate LabView real-time systems

None Demonstrate Isolated high-voltage bench-test (with

low Voltage electronics disconnected)

(3%) Wednesday 1/22/20 - Participate in PLCnext Webinar from Germany on Wednesday,

January 22 at:

3:00am EST which is 9:00am CET (Central European Time)

or 9:00am

EST which is 3:00pm CET (Central European Time)